專用集成電路設(shè)計(jì)實(shí)用教程 從概念到實(shí)現(xiàn)的全流程解析

隨著信息技術(shù)的飛速發(fā)展,專用集成電路(ASIC)在通信、人工智能、汽車電子、消費(fèi)電子等領(lǐng)域的應(yīng)用日益廣泛。與通用集成電路不同,ASIC針對(duì)特定應(yīng)用場(chǎng)景進(jìn)行定制化設(shè)計(jì),具有高性能、低功耗和小面積等優(yōu)勢(shì)。本文將從實(shí)用角度出發(fā),系統(tǒng)介紹ASIC設(shè)計(jì)的基本流程、核心工具與關(guān)鍵技術(shù),為初學(xué)者和從業(yè)者提供一份簡(jiǎn)明實(shí)用的參考指南。

一、ASIC設(shè)計(jì)基礎(chǔ):概念與分類

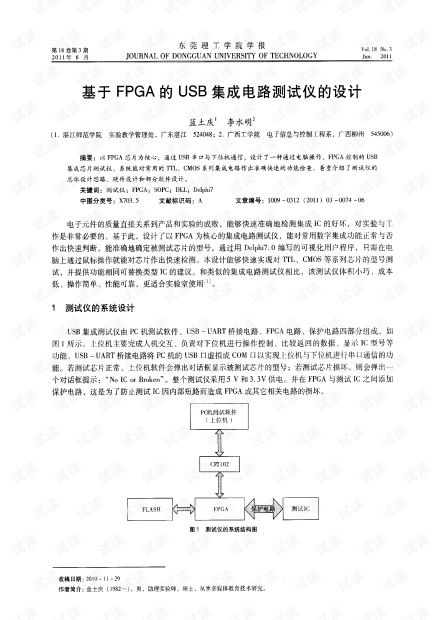

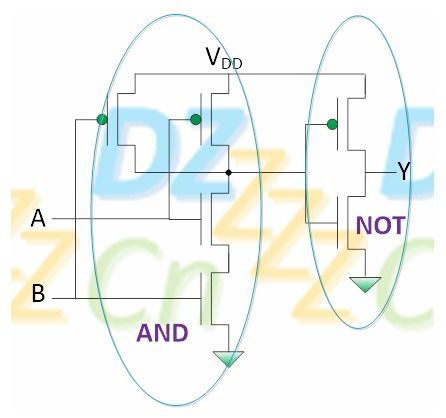

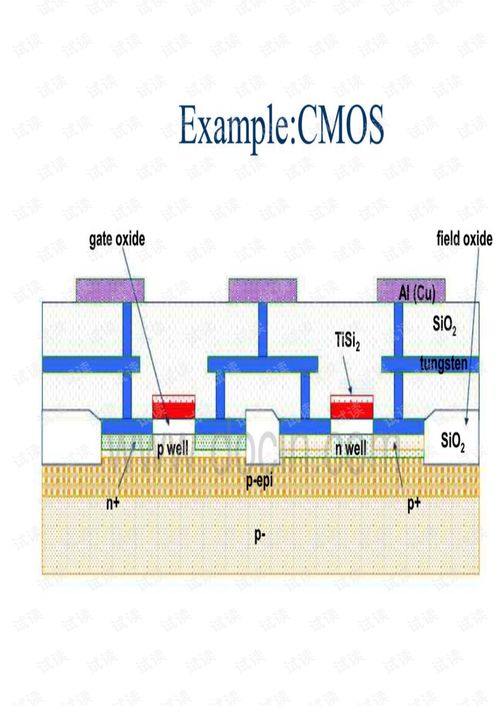

ASIC設(shè)計(jì)是根據(jù)特定需求,從邏輯功能定義到物理實(shí)現(xiàn)的全過程。根據(jù)設(shè)計(jì)靈活性和開發(fā)成本,ASIC可分為全定制、半定制和可編程邏輯器件(如FPGA)。全定制ASIC性能最優(yōu)但開發(fā)周期最長(zhǎng);半定制ASIC基于標(biāo)準(zhǔn)單元庫(kù),平衡了性能與開發(fā)效率;而FPGA則適合原型驗(yàn)證和小批量生產(chǎn)。設(shè)計(jì)者需根據(jù)項(xiàng)目需求、預(yù)算和時(shí)間等因素選擇合適的方案。

二、設(shè)計(jì)流程概覽:從規(guī)格到流片

一個(gè)完整的ASIC設(shè)計(jì)流程通常包括以下階段:

- 規(guī)格定義:明確芯片功能、性能指標(biāo)、接口協(xié)議和功耗要求,形成設(shè)計(jì)規(guī)范文檔。

- 架構(gòu)設(shè)計(jì):確定系統(tǒng)架構(gòu)、模塊劃分、總線結(jié)構(gòu)和時(shí)鐘方案,進(jìn)行算法建模與仿真。

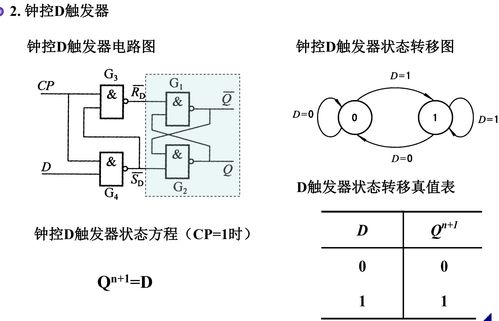

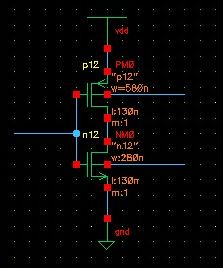

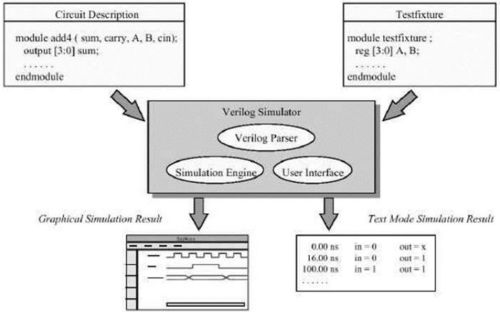

- 前端設(shè)計(jì):使用硬件描述語(yǔ)言(如Verilog或VHDL)進(jìn)行寄存器傳輸級(jí)(RTL)設(shè)計(jì),完成功能仿真和邏輯綜合。

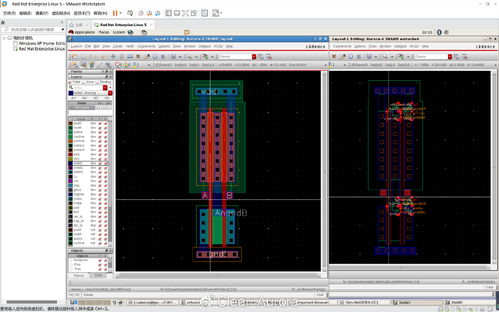

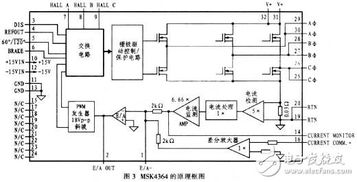

- 后端設(shè)計(jì):包括布局規(guī)劃、時(shí)鐘樹綜合、布線、物理驗(yàn)證和時(shí)序收斂,最終生成用于制造的GDSII文件。

- 流片與測(cè)試:將設(shè)計(jì)交付晶圓廠制造,并對(duì)返回的樣品進(jìn)行功能、性能和可靠性測(cè)試。

三、關(guān)鍵技術(shù)與工具鏈

現(xiàn)代ASIC設(shè)計(jì)高度依賴電子設(shè)計(jì)自動(dòng)化(EDA)工具。前端常用工具包括Synopsys VCS(仿真)、Design Compiler(綜合);后端工具包括Cadence Innovus(布局布線)和Synopsys IC Compiler。設(shè)計(jì)者需掌握以下關(guān)鍵技術(shù):

- 低功耗設(shè)計(jì):采用時(shí)鐘門控、電源門控、多電壓域等技術(shù)降低功耗。

- 時(shí)序收斂:通過約束設(shè)置、優(yōu)化策略確保電路滿足時(shí)序要求。

- 可測(cè)性設(shè)計(jì):插入掃描鏈、內(nèi)建自測(cè)試(BIST)結(jié)構(gòu),提升芯片可測(cè)試性。

- 信號(hào)完整性:分析串?dāng)_、電遷移等效應(yīng),保障電路可靠性。

四、實(shí)用建議與常見挑戰(zhàn)

對(duì)于初學(xué)者,建議從FPGA原型開發(fā)入手,逐步深入ASIC設(shè)計(jì)。在實(shí)際項(xiàng)目中,需特別注意:

- 充分驗(yàn)證:搭建多層次驗(yàn)證環(huán)境,包括單元測(cè)試、集成測(cè)試和系統(tǒng)級(jí)仿真。

- 團(tuán)隊(duì)協(xié)作:明確設(shè)計(jì)規(guī)范與接口,使用版本控制系統(tǒng)(如Git)管理代碼。

- 成本控制:合理選擇工藝節(jié)點(diǎn)(如28nm、14nm),平衡性能、面積與流片費(fèi)用。

- 應(yīng)對(duì)挑戰(zhàn):深亞微米工藝下的物理效應(yīng)(如工藝偏差、寄生參數(shù))需通過仿真與迭代優(yōu)化解決。

五、未來(lái)趨勢(shì)與學(xué)習(xí)資源

隨著工藝進(jìn)步,ASIC設(shè)計(jì)正朝著3D集成、異構(gòu)計(jì)算和智能化設(shè)計(jì)方向發(fā)展。建議設(shè)計(jì)者關(guān)注開源EDA工具(如OpenROAD)、敏捷開發(fā)方法,并持續(xù)學(xué)習(xí)新技術(shù)。推薦參考書籍:《CMOS VLSI Design》《ASIC Design and Synthesis》,同時(shí)可參與IEEE會(huì)議、在線課程(如Coursera的“VLSI CAD”系列)提升實(shí)戰(zhàn)能力。

ASIC設(shè)計(jì)是一門融合了工程技術(shù)與藝術(shù)創(chuàng)造的學(xué)科。通過系統(tǒng)掌握設(shè)計(jì)流程、熟練使用工具鏈,并積累項(xiàng)目經(jīng)驗(yàn),設(shè)計(jì)者能夠?qū)?chuàng)新想法轉(zhuǎn)化為高性能、高可靠的芯片產(chǎn)品,推動(dòng)科技進(jìn)步與應(yīng)用落地。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.xaomwiu.cn/product/32.html

更新時(shí)間:2026-01-11 10:04:45